# ナノワイヤ/CMOS 異種技術集積化

和保 孝夫

#### 1. 研究目的

新規ナノ構造によって革新的な光・電子デバイス、電子-光融合デバイスの研究を推進し、21世紀の低消費電力、高機能システム構築のための光・電子ナノデバイスの基盤技術を開拓する。

本課題では、本拠点内で成長した InAs ナノワイヤを用いて、新たにナノワイヤ /CMOS 異種技術集積化に取り組み、新機能創成の可能性を探索する。特に、(1) InAs ナノワイヤ堆積位置制御技術を確立し、化合物半導体 HEMT を含む小規模集積回路レベルでその有効性を検証すること、(2) ナノワイヤと組み合わせるための低消費電力 CMOS 回路を設計/試作し性能評価すること、(3) それらに基づき、ナノワイヤと CMOS 基板を組み合わせた集積回路を実現し、新機能センサへの応用可能性を探索すること、を目的とした。

# 2. 研究方法

InAs ナノワイヤは Au 微粒子(直径 50nm)をシーズとする VLS モード MOVPE 法で GaAs(111)B 基板上に成長した。ナノワイヤの位置制御堆積に関しては、誘電泳動現象 に基づく電界支援自己整合プロセス(Field-Assisted Self-Assembly: FASA)を用いた。ナノワイヤを用いたデバイスとしては、従来から成長基板をそのまま利用する縦型デバイスの例もあるが、本研究では、成長に用いた基板からナノワイヤを剥離して、回路を搭載した別の基板上に堆積させる横型デバイス構造を対象とした。その理由は、個別素子で用いる場合には縦型でも良いが、集積回路の一部としてナノワイヤを組み込む場合には、ナノワイヤ成長条件と集積回路作製条件とをそれぞれ独立に最適化する必要があるためである。別基板に堆積させるには、予め作り込んだ回路とナノワイヤとの位置合わせが必須であり、FASA 技術で位置制御を行った。

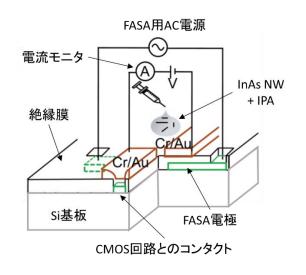

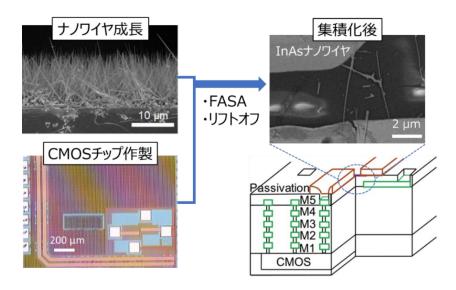

図1は FASA の例を示す。成長基板をイソプロピルアルコール(IPA)に浸して InAs ナノワイヤを削ぎ取り、IPA と共に Si 基板上に滴下する。先ず、標準的な CMOS 製造工程における最上部の配線層を FASA 用の電極として使用し、外部から  $10 \, V_{pp}$ 、 $100 \, kHz$  の AC 電圧を印加した。その結果生じた電界により、FASA 電極に設けたギャップの直上にナノワイヤを集中的に堆積させた。次に、Si 基板に予め作製した CMOS 回路と Cr/Au 配線で接続した。このような 2 段階プロセスを用いることで、FASA 時の AC 電圧印加による CMOS 回路破壊を防いだ。また、堆積過程をモニタするときには Cr/Au 配線を先に形成し、ナノワイヤ堆積に伴う電流変化を測定した。

図1 電界支援自己整合プロセス (FASA)。

CMOS 回路に関しては回路シミュレータを用いた設計とレイアウト検証を行った後、外部ファウンドリにて 0.18µm の標準プロセスを用いた試作を行った。アナログ回路としては CMOS 技術と相性が良いスイッチトキャパシタ方式を採用した。この方式では通常オペアンプを用いるが、定常的に流れる電流のため消費電力削減が困難であった。本研究では、ダイナミックに電流を遮断できる回路を設計し、低消費電力化を図った。

これらの技術に基づき、CMOS 回路を搭載した Si 基板上に InAs ナノワイヤを堆積させ、両者を相互に接続することで異種技術集積回路を実現した。新機能センサに関しては、液体接触によるナノワイヤの抵抗変化を利用することとし、生体/バイオセン

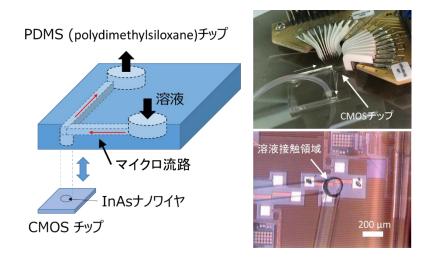

シング分野への応用可能性を検討した。CMOS 基板にはアナログ/デジタル(A/D)変換器の一種である  $\Delta\Sigma$  変調器を搭載し、ナノワイヤとチップ上で直結し、チップ外への出力をデジタル化することで抵抗値測定の高精度化を図った。さらに、CMOS 基板上のナノワイヤ堆積部分だけに液体を流すため、ラボオンチップ(Lab-on-a-Chip)の分野で使われているマイクロ流路チップを作製し、CMOS 基板に装着した。その結果、パッドや端子部分への液体濡れを防ぎ、測定精度と安定性を向上させた。

InAs ナノワイヤ成長に関しては、本拠点内の下村研究室と共同で進めた。また、FASA 技術と HEMT との集積化に関しては Duisburg 大学(ドイツ)と協力して進めた。ナノワイヤ/CMOS 集積化プロセスに関しては本拠点内の中岡研究室の、バイオセンシングへの応用検討で使用した細胞培養液に関しては、学科内の生命系研究室(笹川研究室)の、それぞれ協力を得た。

# 3. 研究成果

# (1) ナノワイヤの電界支援自己整合プロセス(FASA)と HEMT との集積化

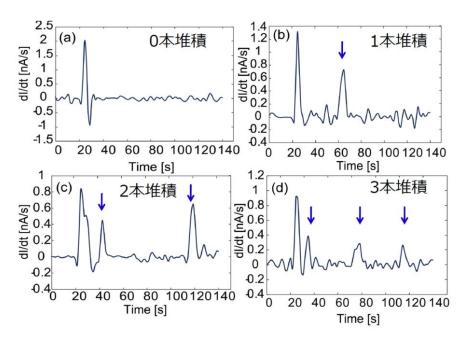

VLS モード MOVPE 法によって作製された InAs ナノワイヤおよび InAs/InP コアシェル型ナノワイヤを用いて、電界支援自己整合プロセス(Field-Assisted Self-Assembly: FASA)によりInP 基板上および Si 基板上に InAs ナノワイヤを堆積させた\*e-i。図 2 は FASA 堆積過程における電流変化を測定した結果である。矢印で示したピーク数が堆積したナノワイヤ本数と一致することが確認できた。また、ピーク出現時刻は、顕微鏡で観察した堆積タイミングとほぼ一致することが分かった。これらの結果から、FASA における微少電流変化を測定することで、ナノワイヤ堆積過程をモニタできる可能性を見いだした\*e-ii。なお、図中で20 秒前後の矢印のないピークは、IPA 滴下に伴うコンダクタンス増加に対応するもので、ナノワイヤ堆積とは無関係である。

図2 FASA 過程のモニタ。

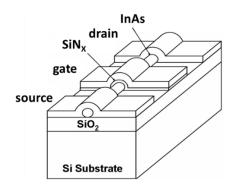

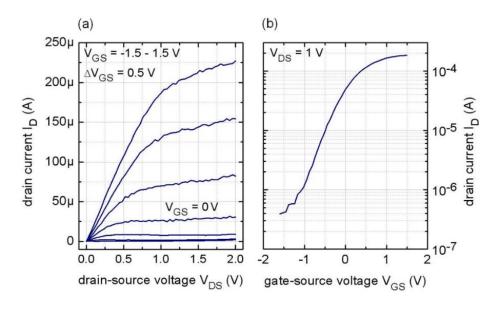

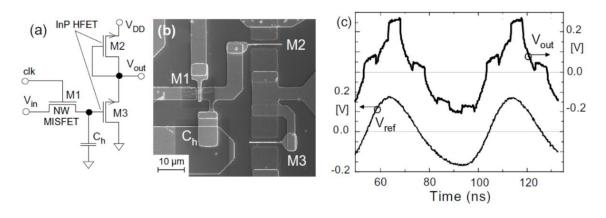

FASA を用いて堆積させたナノワイヤを用いて MISFET を作製し、さらに InP 系 HEMT (High-Electron-Mobility Transistor) と組み合わせてサンプル/ホールド(S/H)回路を作製した。図 3 は回路に使用した MISFET の構造を示す。InAs ナノワイヤをチャネルに用いた。図 4 はその特性を示す。良好なデプリーション型 MISFET が得られることが分かった。試作した S/H 回路の 100 MHz サンプリング動作を図 5 に示す\*e-i。S/H 回路としての正常な回路動作が得られたことから、小規模集積回路レベルで FASA 技術の有効性を実証することができた。

図3 InAs ナノワイヤをチャネルに用いた MISFET。

図 4 InAs ナノワイヤ MISFET の (a)出力特性と(b)伝達特性。

図 5 InAs ナノワイヤ MISFET を用いたサンプル/ホールド(S/H)回路。(a)回路図と(b)チップ写真、(c)動作波形。

# (2) ダイナミック積分器を用いた低消費電力 ΔΣ 変調器

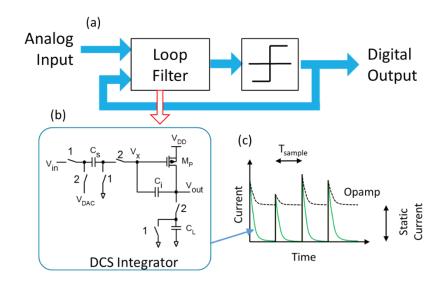

高分解能低消費電力 A/D 変換に適した C 級インバータ  $\Delta$   $\Sigma$  変調器を設計し、ファウンドリサービスを利用した CMOS 回路試作により基本動作を確認した\*e-iii。さらに、一層の低消費電力動作に適したダイナミック共通ソース(Dynamic Common-Source: DCS)回路を搭載した新しい  $\Delta$   $\Sigma$  変調器の設計した\*e-iv。図 6 に  $\Delta$   $\Sigma$  変調器のブロック図と DCS 積分器の回路図、その特性の概略図を示す。 $T_{\text{sample}}$  はサンプリング周期で、従来のオペアンプではサ

ンプリング間で定常電流が流れていたのに対して、提案回路ではサンプリング間で回路に 流れる電流を自動的に遮断し、低消費電力動作を実現した。

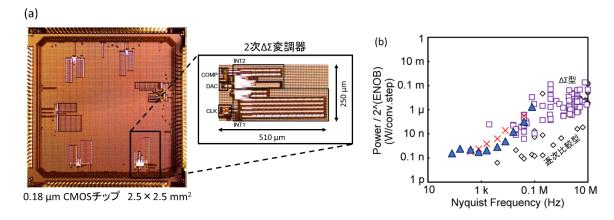

図 7 は試作した CMOS チップ写真と消費電力評価結果を示す。図 7(b)で分かるように、従来の報告例と比較して、今回提案した  $\Delta \Sigma$  変調器では、センサ用途として重要な低周波数領域で最小の消費電力で動作することが分かった\*e-v。逐次比較型 A/D 変換器に関しては低消費電力動作に優れているため参考のためプロットしたが、 $\Delta \Sigma$  変調器と比較して分解能が劣るため、本研究目的には適さないと判断し、検討対象から除外した。

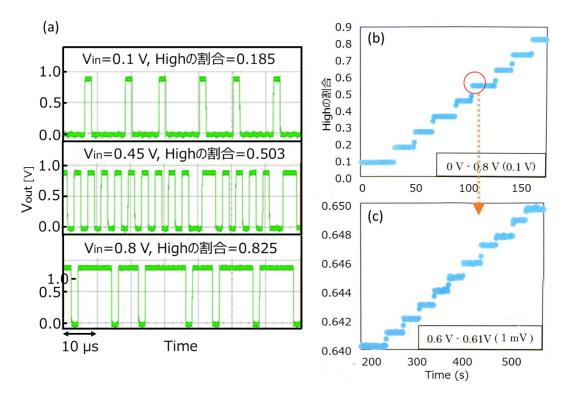

図 8 は回路動作波形と、入出力特性を示す。入力電圧が増加すると「1」の出力頻度が高くなるという  $\Delta \Sigma$  変調器の特徴であるパルス密度変調波が得られた。すなわち、ある一定の時間間隔で「1」の出現回数を数えることで入力電圧を高精度で測定できる。実際、図8(c)で示すように、1 mV でステップ的に増加する入力電圧を明確に区別できることを確認した。入力フルスケールが 1 V なので、これは約 10 ビット分解能に相当する。

図 6 低消費電力  $\Delta \Sigma$  変調器。(a) ブロック図と(b) ダイナミック共通ソース(DCS)積分器、(c) オペアンプとの電流比較の概略図。

図7 DCS 積分器を用いた ΔΣ 変調器。(a)CMOS チップ写真と(b)性能比較。(b)で縦軸は 1 回の A/D 変換に必要な消費電力、横軸はナイキスト周波数(信号帯域)である。×と Δが 今回の結果。□と◇は従来型の ΔΣ 変調器と逐次比較型 A/D 変換器。

図 8 ΔΣ 変調器の入出力特性。(a)出力波形、および、(b)ステップ的に増加する入力電圧 に対する出力の変化と(c)その拡大図。

# (3) ナノワイヤ/CMOS 集積化による新機能センサの可能性探索

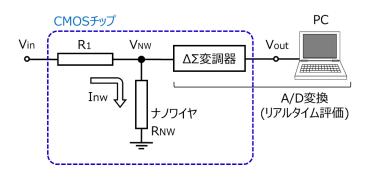

これまでに述べた FASA 技術と低消費電力  $\Delta$   $\Sigma$  変調器に基づき、InAs ナノワイヤ/CMOS 融合型 LSI を作製し、InAs ナノワイヤ両端の電圧変化を  $\Delta$   $\Sigma$  変調器でデジタル値に変換して出力することを可能にした\*e-vi。図 9 は集積化プロセスを示す。CMOS 回路を搭載した Si 基板上に、FASA 技術を用いて、GaAs 基板上に成長した InAs ナノワイヤを堆積した。この図に示すようにナノワイヤは保護膜(Passivation 膜)上にあり、最上部の配線層 M5 を介して CMOS 回路と接続した。図 10 に示すように、CMOS 回路は(2)で述べた  $\Delta$   $\Sigma$  変調器を含み、ナノワイヤ両端の電位差  $V_{NW}$  をパルス密度変調したデジタル信号  $V_{OUT}$  として出力する。PC で時間平均をとりアナログ信号に変換する。時間平均後のサンプリング周波数は 1 kHz とした。

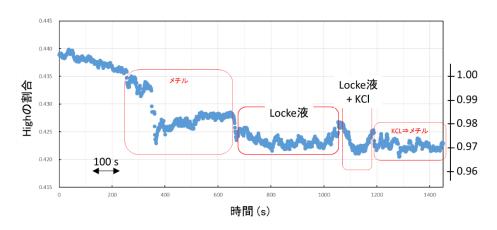

図 11 は Si 基板上のナノワイヤ部分のみに限定的に液体を流すためのマイクロ流路 PDMS チップと、それを Si 基板に装着した様子を示す。右下図の「溶液接触領域」がナノワイヤを堆積した領域である。図 12 は細胞培養液である Locke 液に対するナノワイヤの抵抗変化の様子を示す。90 kHz でオーバサンプリングしたデジタル出力から 1 秒間の「1 (High)」の割合の変化をプロットした。KCL は神経細胞刺激物質として Locke 液に添加して使用される。それぞれの液体の導入により明確な変化が認められた\*e-vii。

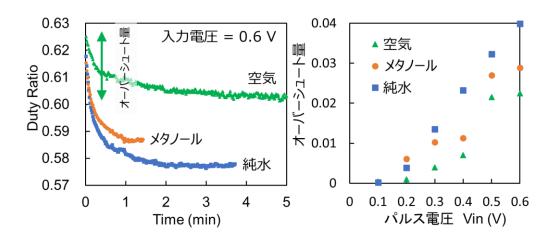

抵抗変化の原因を考察するため、図 10 の  $V_{in}$ にパルス電圧を印加して過渡応答を調べた結果を図 13 に示す。時間と共に出力の「1 (High)」の割合(デューティ比)が低下した。これは図 10 の  $V_{NW}$  が低下したこと、すなわちナノワイヤの抵抗が低下したこと、を意味する。印加したパルス電圧を増加させるとオーバーシュート量も増加すること、また、ナノワイヤを液体に浸した場合にもオーバーシュート量が増加すること、からナノワイヤの抵抗変化が金属的で、抵抗低下は温度低下に起因することが示唆される\*e-viii。従来から指摘されていた表面ピニング状態変化に伴う抵抗変化の可能性とともに、温度変化にも敏感であることを初めて明らかにした。定量的解析は今後の課題であるが、本研究を通じて、ナノワイヤ/CMOS 融合型 LSI のセンサ応用の可能性を明らかにすることができ、当初の目的はほぼ達成できたと考える。

図9 InAs ナノワイヤと CMOS 回路の集積化構造。

図 10 InAs ナノワイヤ抵抗の測定系。 $V_{in}$  は一定とし、ナノワイヤ抵抗変化を電圧  $V_{NW}$  の変化として測定した。 $V_{in}$  ながれる頻度変調波で、その頻度を PC で測定した。

図 11 PDMS チップを InAs ナノワイヤ/CMOS 集積回路に装着し、液体滴下による InAs ナノワイヤ抵抗変化測定を可能にした Lob-on-a-Chip (LOC) 構造。

図 12 InAs ナノワイヤ両端電圧の時間変化の測定例。

図 13 パルス電圧駆動時の InAs ナノワイヤ両端電圧の過途応答とオーバーシュート量の 比較。

特に優れた研究成果、

ΔΣ 変調器を搭載した CMOS 回路基板に InAs ナノワイヤを FASA 堆積させることで InAs/Si 融合回路を作製し、InAs ナノワイヤ両端の電圧変化をデジタル値に変換して出力する回路 動作実験に成功したことは初めてである\*e-iv。従来からオペアンプなどの簡単な CMOS 回 路とカーボンナノチューブ(CNT)を組み合わせた例はあったが、A/D 変換という高機能 CMOS 回路( $\Delta\Sigma$  変調器)と InAs ナノワイヤをモノリシックに集積化し、回路動作を実現したのはこれまでに例がない。InAs は表面に電子密度の高い反転層が形成されているため、バックゲートなしでも良好な伝導特性が得られるため素子構造が簡単化できた。また、表面への化学物質の吸着や、液体の流量変化で伝導率が大きく変わる可能性があり、それを CMOS 回路でデジタル的に検知する高感度低消費電力センサの実現に見通しが得られた。

要素技術としては、(1)マイクロ流路チップの装着により測定精度と安定性を改善できたこと、(2)ファウンドリ提供の CMOS 基板へのナノワイヤ堆積技術の有効性を集積回路レベルで検証できたこと、(3)センサ用途で重要な低サンプリング周期領域において ΔΣ 変調器の低消費電力化を実現したこと、を挙げることができる。

## 研究成果の副次的効果

今回実現したナノワイヤ/CMOS融合回路は、従来型ラボオンチップ(LOC)に CMOSチップを組み込んだ次世代型ラボオンチップと見なせる。3桁以上のA/D変換精度が見込めるため、微細なナノワイヤ抵抗変化の直接測定が可能である。今回、細胞培養液などの各種液体に対するナノワイヤの応答が確認できたことで、ナノ構造の物性解明への応用だけでなく、神経伝達物質の高精度モニタなど、生体/バイオセンサへの応用が期待できる。

今回低消費電力動作に成功した  $\Delta \Sigma$  変調器に用いた DCS 回路は、従来からオペアンプを使用してきた多くのアナログ回路に適用可能である。動作終了後自動的にパワーダウンする発想はシステム LSI におけるパワーマネジメントと同じ発想であり、今後、多くのアナログ回路への応用が期待できる。

#### 研究発表リスト

## 雑誌論文

- e1. 石田宇一, <u>和保孝夫</u>、「キャパシタアレイ回路を用いた粘菌コンピューティングの基礎検討」、多値論理研究ノート 第 37 巻 No. 7 pp. 7-1 7-5 2014 年 査読無し

- e2. \*e-iv Ryo Matsushiba, Hiroaki Kotani, <u>Takao Waho</u>, "An Energy-Efficient ΔΣ Modulator Using Dynamic-Common-Source Integrators," IEICE Trans. Electronics, Vol .E97-C, No. 05, May 2014.

- e3. \*ei <u>和保 孝夫</u> 「ナノワイヤの堆積プロセスと回路応用」 応用物理(最近の展望) 第 81 巻 第 12 号 pp.1015-1019 (2012)

- e4. \*e-i Kai BLEKKER, René RICHTER, Ryosuke ODA, Satoshi TANIYAMA, Oliver BENNER, Gregor KELLER, B. MÜNSTERMANN, Andrey LYSOV, Ingo REGOLIN, <u>Takao WAHO</u>, Werner PROST, "InAs nanowire circuits fabricated by field-assisted self-assembly on a host substrate," IEICE Trans. on Electronics, Vol. E95-C, No. 8, pp. 1369 1375, 2012.

- e5. 栗栖裕樹, <u>和保孝夫</u>、「冗長性を持つ逐次近似 A/D 変換器の設計」 多値論理研究 / ート、第 35 巻、no. 13, pp. 13-1 13-6 2012 年 査読無し

- e6. \*e-iv Ryoto Yaguchi, Fumiyuki Adachi, <u>Takao Waho</u>, "A Dynamic Source-Follower Integrator and Its Application to  $\Delta\Sigma$  Modulators," IEICE Trans. on Electronics, vol. E94-C, no. 5, pp. 802 806, 2011.

- e7. 佐々木 達也、<u>和保 孝夫</u>、「高エネルギー使用効率容量アレイを用いた逐次比較 A/D 変換器」、多値論理研究ノート、第 34 巻、no. 12, pp. 12-1 12-6、2011 年、査読無し

## 図書

1. <u>和保孝夫</u>、「ナノワイヤ最新技術の基礎と応用展開」(監修:福井孝志)シーエムシー出版 240ページ 第 III 編第 2 章回路応用

## 学会発表

- e8. \*e-iv 小原一馬· 和保孝夫 「能動/受動併用ダイナミック積分器を用いた低消費電力  $\Delta \Sigma$  変調器」電子情報通信学会総合大会講演論文集 C-12-18 九州大学 福岡 2016年3 月 16日

- e9. \*e-viii 島本一成·多田共史.荻野雄大·朝倉啓太·<u>下村和彦</u>·<u>和保孝夫</u>「InAs ナノワイヤ /CMOS 集積回路の LOC への応用」電子情報通信学会総合大会講演論文集 C-10-13 九州大学 福岡 2016年3月15日

- e10. 山崎雄介・小原一馬・<u>和保孝夫</u>「シリアル DAC を用いた逐次比較型 A/D 変換器の設計」電子情報通信学会総合大会講演論文集 A-1-17 九州大学 福岡 2016年3月15日

- e11. 石田宇一・和保孝夫「粘菌コンピューティングを模したニューラルネットワーク型

- A/D 変換器」電子情報通信学会技術研究報告. ED, 電子デバイス研究会 2016年3月4日

- e12. <u>和保 孝夫</u>、石田 宇一「ニューラルネットを用いた A/D 変換器」第 29 回多値論理とその応用研究会 電子情報通信学会 MVL16-10 2016 年 1 月 10 日

- e13. \*e-vii <u>Takao Waho</u>, "InAs-Nanowire/CMOS Co-Integration for Sensor Applications," BIT's 5th Nano Science and Technology 2015, Euro Asia Economic forum 2015, Xian, China, Sept. 25, 2015.

- e14. \*e-vii\_Issei Shimamoto, Kazuma Ohara, Takehiro Ogino, Kazuhiko Shimomura, and <u>Takao Waho</u>, "InAs Nanowire Resistance Measurement Using Nanowire/CMOS Co-Integrated Circuit," 11th Topical Workshop on Heterostructure Microelectronics, August 23 26, 2015.

- e15. U. Ishida, Y. Yamazaki and <u>T. Waho</u>, "Non-Binary Analog-to-Digital Converter Based on Amoeba-Inspired Neural Network," Proc. Multiple-Valued Logic (ISMVL), 2015 IEEE International Symposium on Multiple-Valued Logic (ISMVL), pp. 103 108, May 18 20 2015.

- e16. <u>T. Waho</u>, K. Ohara, "Analog Circuits for Low-Power Data Converters," Proc. 24th International Workshop on Post-Binary ULSI Systems, pp. 2 5, May 17, 2015.

- e17. \*e-iv 小原一馬・松芝 亮・<u>和保孝夫</u>「ダイナミック積分器を用いた 2 次  $\Delta$   $\Sigma$  変調器」、2015 年電子情報通信学会総合大会 C-12-31 立命館大学 びわこ・くさつキャンパス (草津市、滋賀県)、2015 年 3 月 10 日~13 日

- e18. \*e-vii 島本一成・細野 優・小原一馬・<u>和保孝夫</u>・荻野雄大・<u>下村和彦</u>「InAs ナノワイヤ/CMOS 異種技術集積化とセンサ応用の可能性」、2015 年電子情報通信学会総合大会 C-10-14 立命館大学 びわこ・くさつキャンパス (草津市、滋賀県)、2015年3月10日~13日

- e19. 山﨑雄介・<u>和保孝夫</u>「チャージシェア型非 2 進 SAR ADC の設計」、2015 年電子情報 通信学会総合大会 A-1-26 立命館大学 びわこ・くさつキャンパス (草津市、滋 賀県)、2015 年 3 月 10 日~13 日

- e20. 石田宇一, 山﨑雄介, <u>和保孝夫</u> 「粘菌ニューラルネット回路を用いた A/D 変換器」、多値論理とその応用研究会 研究技術報告 vol. MVL-15, no. 1, pp. 39 44 (第 28 回多値論理とその応用研究会 那覇市 沖縄県、2015 年 1 月 10 日~11 日)

- e21. \*e-iv\_Matsushiba, R.; Ohara, K.; Waho, T., "An energy-efficient dynamic-integrator-based  $\Delta\Sigma$  modulator," Proc. 2014 21st IEEE International Conference on Electronics, Circuits and Systems (ICECS), pp. 467 470, Marseille, France, 2014.

- e22. \*e-iv 小原一馬・松芝 亮・<u>和保孝夫</u>、「レベルシフト型ダイナミック共通ソース積分器を用いた低消費電力 2 次  $\Delta$   $\Sigma$  変調器」、2014年電子情報通信学会ソサエティ大会 A-1-11 徳島大学 常三島キャンパス、2014年9月23日~26日

- e23. <u>Takao Waho</u>, "Non-binary Successive Approximation in Analog-to-Digital Converters: A Survey," Proc. 44th IEEE Int. Symp. Multiple-Valued Logic (ISMVL2014), pp. 73 78, Bremen, Germany, 19 22 May 2014.

- e24. \*e-vi Kenji Michimata, Hiroaki Kotani, Tatsuro Watanabe, Hiroaki Funayama, Shin Murakami, Kazuhiko Shimomura, and Takao Waho, "Heterogeneous Integration of an InAs Nanowire with Energy-Efficient CMOS Delta-Sigma Modulator, "IEEE SENSORS 2013, Baltimore, Maryland, USA, November 4-6, 2013.

- e25. \*e-iv Ryo Matsushiba, Hiroaki Kotani, <u>Takao Waho</u>, "An Energy-Efficient Delta-Sigma Modulator Using Dynamic-Common-Source Integrators," Proc. 21st European Conference on Circuit Theory and Design (ECCTD), Dresden, Germany, September 8-12, 2013.

- e26. \*e-i W. Prost, F.-J. Tegude, and <u>T. Waho</u>, "InAs and GaAs nanowires for electronics and optoelectronics (Invited)," 10th Topical Workshop on Heterostructure Microelectronics (TWHM), Hakodate, Japan, September 2 5, 2013, Paper #2-2.

- e27. \*e-v K. Michimata, H. Kotani, T. Watanabe, H. Funayama, S. Murakami, <u>K. Shimomura</u>, and <u>T. Waho</u>, "InAs-Nanowire CMOS Heterogeneous Integration Using Field-Assisted Self-Assembly," 10th Topical Workshop on Heterostructure Microelectronics (TWHM), Hakodate, Japan, September 2 5, 2013, Paper #2-10.

- e28. \*e-iv Ryo Matsushiba, Yuri Yamaguchi, Hiroaki Kotani, <u>Takao Waho</u>, "Design of a Power-Efficient Delta-Sigma Modulator Using Dynamic Integrators," Proc. 2013 Asia-Pacific Workshop on Fundamentals and Applications of Advanced Semiconductor Devices (AWAD), 2B-7, Seoul, Korea, June 26 28, 2013.

- e29. Yuki Kurisu, Tatsuya Sasaki and <u>Takao Waho</u>, "A Successive Approximation A/D Converter Using Generalized Non-Binary Algorithm," Proc. 43rd IEEE Int. Symp. Multiple-Valued Logic (ISMVL), pp. 152 157, Toyama, Japan, 22 24 May 2013, Page(s): 152 157.

- e30. \*e-iv Ryo Matsushiba, Hiroto Kotani, Ryoto Yaguchi, and <u>Takao Waho</u>, "A 2nd -Order Delta-Sigma Modulator Using Dynamic-Source-Follower Integrator," Proc. 22th International Workshop on Post-Binary ULSI Systems, pp. 41 42, Toyama, Japan, May 21, 2013, Page(s): 203 207.

- e31. \*e-iv 松芝 亮・矢口僚人・<u>和保孝夫</u>、「ダイナミック積分器を用いた低消費電力 2 次 ΔΣ 変調器」、2013 年電子情報通信学会総合大会、岐阜、A-1-17、2013 年 3 月 20 日

- e32. \*e-iii 小谷博亮・松芝 亮・和保孝夫、「弱反転インバータ積分器を用いた低消費電力 ΔΣ変調器」、2013 年電子情報通信学会総合大会、岐阜、C-12-68、2013 年 3 月 22 日

- e33. \*e-v 船山裕晃・渡邉龍郎・道又賢司・村上 新・<u>下村和彦</u>・<u>和保孝夫</u>、「InAs ナノワイヤの電界アシスト自己整合堆積プロセス」電子情報通信学会 電子デバイス研究会、信学技報、2013年2月27日

- e34. \*e-iii 小谷博亮、矢口僚人、<u>和保孝夫</u>、「弱反転インバータ積分器を用いた低消費電力 Δ∑変調器の試作評価」電子情報通信学会 第 26 回多値論理とその応用研究会、東 京、2013 年 1 月 12 日、vol. MVL13, No.1, pp. 51 – 55

- e35. Akinori Moriyama, Satoshi Taniyama, <u>Takao Waho</u>, "A Low-Distortion Switched-Source-Follower Track-and-Hold Circuit," 19th IEEE International Conference on Electronics, Circuits, and Systems (ICECS), Seville, Spain, December 9-12, 2012, Page(s): 105 108.

- e36. <u>Takao Waho</u>, "InAs Nanowire Circuit Applications," Nano Science & Technology 2012, Qindao, China, October 26-28, 2012

- e37. 松芝 亮・矢口僚人・<u>和保孝夫</u> 「利得調整可能なダイナミック・ソースフォロワ積 分器」 電子情報通信学会 2012 年ソサエティ大会、A-1-3、富山大学 2012 年 9 月 11 日~14 日

- e38. 佐々木達也・<u>和保孝夫</u> 「冗長 Junction-Splitting 容量アレイを用いた SAR ADC」 電子情報通信学会 2012 年ソサエティ大会、A-1-5、富山大学 2012 年 9 月 11 日~14 日

- e39. \*e-ii 道又賢司・船山裕晃・渡邉龍郎・村上 新・<u>下村和彦</u>・<u>和保孝夫</u> 「InAs ナノワイヤの Si 基板上への電界アシスト自己整合堆積」 電子情報通信学会 2012 年ソサエティ大会、C-10-1、富山大学 2012 年 9 月 11 日~14 日

- e40. \*e-iii Hiroaki Kotani, Ryoto Yaguchi, <u>Takao Waho</u>, "Energy Efficiency of Multi-bit delta-sigma Modulators Using Inverter-based Integrators," Proc. 42nd IEEE Int. Symp. Multiple-Valued Logic (ISMVL), pp. 203 207, Victoria, B. C., Canada, 14 16 May 2012.

- e41. 矢口僚人、安達美志、和保孝夫、「ダイナミック・ソースフォロア積分器を用いた低

- 消費電力 2 次  $\Delta\Sigma$  変調器」、2012 年電子情報通信学会総合大会、C-12-50、岡山、2012 年 3 月 22 日

- e42. 小野大騎、遠山雄二、<u>和保孝夫</u>、「高速 D/A 変換器における高調波歪の評価」、2012 年電子情報通信学会総合大会、A-1-43、岡山、2012 年 3 月 23 日

- e43. 馬場健人、遠山雄二、<u>和保孝夫</u>、「デュアルカウント方式を用いた時間領域 A/D 変換器の設計」、2012年電子情報通信学会総合大会、A-1-44、岡山、2012年3月23日

- e44. 森山顕矩、谷山 諭、<u>和保孝夫</u>、「高速低歪み HEMT サンプルホールド回路の設計」、2012年電子情報通信学会総合大会、C-10-10、岡山、2012年3月23日

- e45. \*e-i <u>和保孝夫</u>、Werner Prost、「InAs ナノワイヤの回路応用(招待講演)」、第 59 回応 用物理学関係連合講演会、15p-B3-2、東京、2012 年 3 月 15 日

- e46. <u>和保孝夫</u>、「A/D変換における雑音抑制技術(依頼講演)」、電子情報通信学会 電子デバイス研究会、特別ワークショップ、東京、2012年3月2日

- e47. 渡邉龍郎、乙幡 温、<u>和保孝夫</u>、「InAs ナノワイヤ MISFET の高周波特性評価」、電子情報通信学会 電子デバイス研究会、信学技報、札幌、2012年2月7日

- e48. <u>和保孝夫</u>、「A/Dインターフェースとしての多値技術(招待講演)」、電子情報通信 学会 第 25 回多値論理とその応用研究会、MVL12-7、宮崎、2012 年 1 月 7 日

- e49. \*e-iii 小谷博亮、矢口僚人、<u>和保孝夫</u>、「インバータを用いた多ビット ΔΣ 変調器における消費電力評価」電子情報通信学会 第 25 回多値論理とその応用研究会、MVL12-14、宮崎、2012 年 1 月 8 日

- e50. \*e-iii 小谷博亮、矢口僚人、<u>和保孝夫</u>、「インバータを用いた  $\Delta \Sigma$  変調器の消費電力評価」、電子情報通信学会 2011 年ソサエティ大会、A-1-33、札幌、2011 年 9 月 1 6 日

- e51. 渡邉龍郎、乙幡 温、<u>和保孝夫</u>、Kai Blekker、 Werner Prost、Franz-Josef Tegude、「InAs ナノワイヤ MISFET の高周波特性評価」、電子情報通信学会 2011 年ソサエティ大会、C-10-5、札幌、2011 年 9 月 1 3 日

- e52. 森山顕矩、谷山 諭、<u>和保孝夫</u>、「DC キャンセルパスを持つスイッチトソースフォロワ型サンプルホールド回路」、電子情報通信学会 2011 年ソサエティ大会、C-10-15、札幌、2011 年 9 月 1 3 日

- e53. \*e-i Kai Blekker, René Richter, Oliver Benner, B. Münstermann, Andrey Lysov, Ingo Regolin, Werner Prost, Ryosuke Oda, Satoshi Taniyama, <u>Takao Waho</u>, "InAs nanowire circuits fabricated by field-assisted self-assembly on a host substrate," 9th Topical Workshop on Heterostructure Microelectronics (TWHM), Gifu, Japan, August 28 31, 2011.

- e54. \*e-i Eisuke Takashima, Hiroaki Funayama, <u>Takao Waho</u>, <u>Kazuhiko Shimomura</u>, and Werner Prost, "Field-Assisted Self-Assembly of InAs Naonwires on Si substrate," 9th Topical Workshop on Heterostructure Microelectronics (TWHM), Gifu, Japan, August 28 31, 2011.

- e55. Keita HOSHI, Kazuhisa NOGUCHI, and <u>Takao WAHO</u>, "Design of Continuous-Time Bandpass Delta-Sigma Modulator Using RTD/HEMT Comparator," Proc. 2011 Asia-Pacific Workshop on Fundamentals and Applications of Advanced Semiconductor Devices (AWAD), Daejeon, Korea, June 29 July 1, 2011.

- e56. \*e-i <u>Takao Waho</u>, Satoshi Taniyama, René Richter, Oliver Benner, Kai Blekker, Werner Prost, "Sample-and-hold circuits using InAs nanowire FETs," Proc. 35th Workshop on Compound Semiconductor Devices and Integrated Circuits (WOCSDICE), Catania, Italy, 29 May - 1 June, 2011

- e57. Kazuki Kuribayashi, Kazuya Machida, Yuji Toyama, <u>Takao Waho</u>, "Time-Domain Multi-bit ΔΣ Analog-to-Digital Converter," Proc. 41st IEEE Int. Symp. Multiple-Valued Logic

(ISMVL), pp. 254 - 258, Tuusula, Finland, 23-25 May 2011, Page(s): 254 - 258. e58. <u>Takao Waho</u>, "Non-Binary Analog-to-Digital Converters (Invited)," Proc. 20th International Workshop on Post-Binary ULSI Systems, pp. 21 - 25, Tuusula, Finland, May 22, 2011.